PCIe 6.0 and the Future of High-Speed Computer Interfaces

The development of PCI Express (PCIe) 6.0 represents a significant milestone in the evolution of computer hardware connectivity. As data-intensive applications such as artificial intelligence, high-performance computing, and cloud infrastructures expand rapidly, the need for higher bandwidth and reduced latency has become critical. PCIe 6.0 aims to double the transfer rate of PCIe 5.0 while maintaining backward compatibility, positioning itself as a key enabler of next-generation computing.

The Technical Advancements of PCIe 6.0

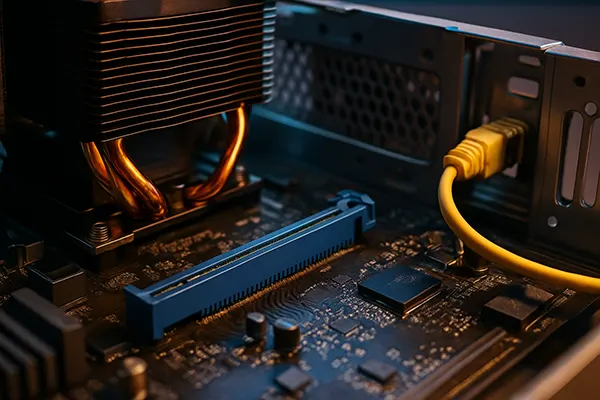

PCIe 6.0 introduces 64 GT/s transfer speeds, doubling the throughput of PCIe 5.0. This advancement is achieved through the use of Pulse-Amplitude Modulation with four levels (PAM4), a technique widely adopted in modern networking technologies. By integrating this signalling method, PCIe 6.0 can provide up to 256 GB/s of bidirectional bandwidth on a 16-lane configuration.

Another notable feature of PCIe 6.0 is the implementation of forward error correction (FEC). Given the increased error rates associated with PAM4 signalling, FEC ensures data integrity without significantly increasing latency. This is particularly crucial for workloads requiring consistent accuracy and reliability, such as scientific computing and machine learning training.

The specification also supports dynamic link equalisation and low-latency operations. These improvements allow PCIe 6.0 to deliver higher performance while reducing bottlenecks in data transfer, ensuring a smoother experience for systems requiring massive parallel data processing.

Compatibility and Integration

A critical strength of PCIe has always been its backward compatibility. PCIe 6.0 continues this tradition, allowing systems to integrate new devices without abandoning legacy hardware. This approach ensures gradual adoption across industries, particularly in environments where infrastructure replacement is costly or impractical.

Hardware manufacturers are already preparing chipsets and processors that support PCIe 6.0. Intel and AMD have announced roadmaps integrating the new standard into upcoming server and desktop CPUs. This level of support signals an accelerated adoption in data centres, gaming systems, and enterprise servers.

Additionally, storage and graphics card manufacturers are expected to embrace PCIe 6.0 as soon as demand for higher data throughput becomes widespread. The balance between innovation and compatibility will remain crucial for its success.

Applications and Industry Impact

PCIe 6.0 will have transformative implications across multiple industries. In data centres, the ability to process larger datasets at higher speeds is essential for supporting artificial intelligence, big data analytics, and high-frequency trading platforms. These fields rely heavily on reducing latency to microseconds.

For consumer markets, PCIe 6.0 will benefit graphics cards, SSDs, and networking devices. Gamers, content creators, and professionals working with 3D rendering or video editing will notice significant improvements in system responsiveness when adopting hardware built on the new interface.

In telecommunications and edge computing, PCIe 6.0 will facilitate faster data handling in distributed networks. With 5G and beyond requiring faster processing at multiple points, PCIe 6.0 will serve as a foundational technology for future digital infrastructures.

Challenges in Adoption

Despite its promise, PCIe 6.0 faces challenges that may delay mass-market adoption. The complexity of PAM4 signalling increases design costs and requires more advanced testing and validation processes. This complexity translates into higher hardware prices, particularly during the early stages of deployment.

Another challenge lies in balancing power consumption with performance. As devices demand higher bandwidth, energy efficiency becomes critical for both mobile and server-grade systems. Manufacturers must innovate to ensure that performance gains do not compromise sustainability and thermal management.

Finally, industry adoption will depend on the availability of real-world applications requiring such speeds. Until workloads consistently demand PCIe 6.0’s full capabilities, its benefits may remain limited to niche markets such as research institutions and high-end enterprise environments.

Future Outlook for High-Speed Interfaces

Looking beyond PCIe 6.0, the industry is already discussing PCIe 7.0, which promises to once again double the data rate. However, the transition to each new standard is becoming increasingly complex and costly, pushing companies to consider hybrid approaches that balance performance with energy efficiency and cost-effectiveness.

High-speed interfaces are also expanding into other domains, such as CXL (Compute Express Link), which builds upon PCIe technology to enable better memory and resource sharing between CPUs, GPUs, and accelerators. This synergy between standards indicates that the future will not be dominated by a single interface but by complementary technologies working together.

By 2030, high-speed interconnects like PCIe 6.0 will be central to artificial intelligence, cloud-native applications, and scientific simulations. Their role will extend beyond traditional computing into new fields such as autonomous vehicles and smart manufacturing systems, where real-time data exchange is vital.

The Role of Standardisation Bodies

The PCI-SIG (PCI Special Interest Group) remains the key organisation driving the development of PCIe. Its collaborative model ensures input from industry leaders, semiconductor companies, and hardware manufacturers, allowing for global adoption of new standards.

Standardisation not only guarantees compatibility across hardware ecosystems but also accelerates innovation by providing a clear roadmap for research and development. PCI-SIG’s efforts ensure that advancements in PCIe technology meet both industry demands and practical implementation challenges.

With PCIe 6.0 now ratified and hardware implementation underway, the standard is poised to play a defining role in the evolution of computing infrastructure throughout the remainder of the decade.