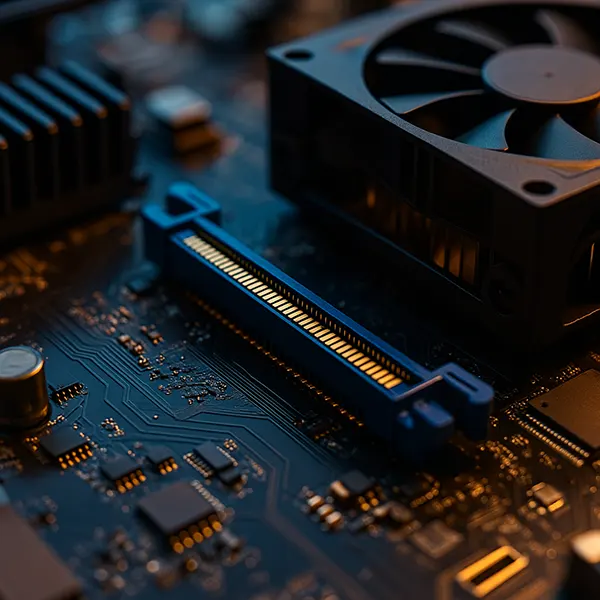

PCIe 6.0 y el futuro de las interfaces informáticas de alta velocidad

El desarrollo de PCI Express (PCIe) 6.0 representa un hito significativo en la evolución de la conectividad del hardware informático. A medida que las aplicaciones intensivas en datos como la inteligencia artificial, la computación de alto rendimiento y las infraestructuras en la nube se expanden rápidamente, la necesidad de mayor ancho de banda y menor latencia se ha vuelto crítica. PCIe 6.0 pretende duplicar la velocidad de transferencia de PCIe 5.0 manteniendo la compatibilidad hacia atrás, posicionándose como un habilitador clave de la informática de próxima generación.

Los avances técnicos de PCIe 6.0

PCIe 6.0 introduce velocidades de transferencia de 64 GT/s, duplicando el rendimiento de PCIe 5.0. Este avance se logra mediante el uso de modulación por amplitud de pulsos en cuatro niveles (PAM4), una técnica ampliamente adoptada en tecnologías modernas de redes. Gracias a esta señalización, PCIe 6.0 puede ofrecer hasta 256 GB/s de ancho de banda bidireccional en una configuración de 16 carriles.

Otra característica destacada de PCIe 6.0 es la implementación de corrección de errores hacia adelante (FEC). Dado el aumento de tasas de error asociadas con la señalización PAM4, el FEC garantiza la integridad de los datos sin aumentar de forma significativa la latencia. Esto resulta especialmente crucial para cargas de trabajo que requieren precisión constante y fiabilidad, como la computación científica y el entrenamiento de modelos de aprendizaje automático.

La especificación también incluye ecualización dinámica de enlace y operaciones de baja latencia. Estas mejoras permiten a PCIe 6.0 ofrecer un rendimiento superior reduciendo los cuellos de botella en la transferencia de datos, garantizando una experiencia más fluida en sistemas que necesitan procesamiento masivo de datos en paralelo.

Compatibilidad e integración

Una fortaleza clave de PCIe siempre ha sido su compatibilidad hacia atrás. PCIe 6.0 mantiene esta tradición, permitiendo que los sistemas integren nuevos dispositivos sin abandonar el hardware heredado. Este enfoque asegura una adopción gradual en sectores donde reemplazar la infraestructura resulta costoso o poco práctico.

Los fabricantes de hardware ya están preparando chipsets y procesadores compatibles con PCIe 6.0. Intel y AMD han anunciado hojas de ruta que integran el nuevo estándar en futuros procesadores de servidor y escritorio. Este nivel de apoyo apunta a una adopción acelerada en centros de datos, sistemas de juego y servidores empresariales.

Además, se espera que los fabricantes de almacenamiento y tarjetas gráficas adopten PCIe 6.0 tan pronto como la demanda de mayor ancho de banda se generalice. El equilibrio entre innovación y compatibilidad seguirá siendo fundamental para su éxito.

Aplicaciones e impacto en la industria

PCIe 6.0 tendrá implicaciones transformadoras en múltiples sectores. En los centros de datos, la capacidad de procesar conjuntos de datos más grandes a mayor velocidad es esencial para soportar inteligencia artificial, análisis de big data y plataformas de trading de alta frecuencia. Estos campos dependen en gran medida de la reducción de la latencia a microsegundos.

En el mercado de consumo, PCIe 6.0 beneficiará a las tarjetas gráficas, SSD y dispositivos de red. Los jugadores, creadores de contenido y profesionales que trabajan con renderizado 3D o edición de vídeo notarán mejoras significativas en la capacidad de respuesta del sistema al adoptar hardware basado en esta interfaz.

En telecomunicaciones y computación perimetral, PCIe 6.0 facilitará un manejo más rápido de los datos en redes distribuidas. Con el 5G y las generaciones futuras exigiendo un procesamiento más veloz en múltiples puntos, PCIe 6.0 será una tecnología fundamental para las infraestructuras digitales del futuro.

Retos en la adopción

A pesar de su potencial, PCIe 6.0 enfrenta desafíos que pueden retrasar su adopción masiva. La complejidad de la señalización PAM4 aumenta los costos de diseño y requiere procesos más avanzados de prueba y validación. Esta complejidad se traduce en precios de hardware más altos, especialmente en las primeras fases de despliegue.

Otro reto consiste en equilibrar el consumo energético con el rendimiento. A medida que los dispositivos demandan más ancho de banda, la eficiencia energética se vuelve crítica tanto para sistemas móviles como para servidores. Los fabricantes deberán innovar para garantizar que las mejoras de rendimiento no comprometan la sostenibilidad ni la gestión térmica.

Por último, la adopción dependerá de la disponibilidad de aplicaciones reales que necesiten tales velocidades. Hasta que las cargas de trabajo demanden de forma constante todas las capacidades de PCIe 6.0, sus beneficios podrían limitarse a mercados especializados como instituciones de investigación y entornos empresariales de gama alta.

Perspectivas futuras de las interfaces de alta velocidad

Más allá de PCIe 6.0, la industria ya discute PCIe 7.0, que promete duplicar nuevamente la velocidad de transferencia. Sin embargo, cada transición a un nuevo estándar se vuelve cada vez más compleja y costosa, lo que impulsa a las compañías a considerar enfoques híbridos que equilibren rendimiento, eficiencia energética y rentabilidad.

Las interfaces de alta velocidad también se están expandiendo hacia otros dominios, como CXL (Compute Express Link), que se basa en la tecnología PCIe para mejorar el uso compartido de memoria y recursos entre CPUs, GPUs y aceleradores. Esta sinergia entre estándares indica que el futuro no estará dominado por una sola interfaz, sino por tecnologías complementarias que funcionen en conjunto.

Para 2030, los interconectores de alta velocidad como PCIe 6.0 serán centrales en la inteligencia artificial, las aplicaciones nativas en la nube y las simulaciones científicas. Su papel se extenderá más allá de la informática tradicional hacia campos emergentes como los vehículos autónomos y la manufactura inteligente, donde el intercambio de datos en tiempo real es vital.

El papel de los organismos de estandarización

El PCI-SIG (PCI Special Interest Group) sigue siendo la organización clave que impulsa el desarrollo de PCIe. Su modelo colaborativo garantiza la participación de líderes de la industria, empresas de semiconductores y fabricantes de hardware, lo que facilita la adopción global de los nuevos estándares.

La estandarización no solo asegura la compatibilidad entre ecosistemas de hardware, sino que también acelera la innovación al proporcionar una hoja de ruta clara para la investigación y el desarrollo. Los esfuerzos del PCI-SIG aseguran que los avances en la tecnología PCIe respondan tanto a las demandas de la industria como a los desafíos de implementación práctica.

Con PCIe 6.0 ya ratificado y con la implementación de hardware en marcha, el estándar está listo para desempeñar un papel decisivo en la evolución de la infraestructura informática durante el resto de la década.