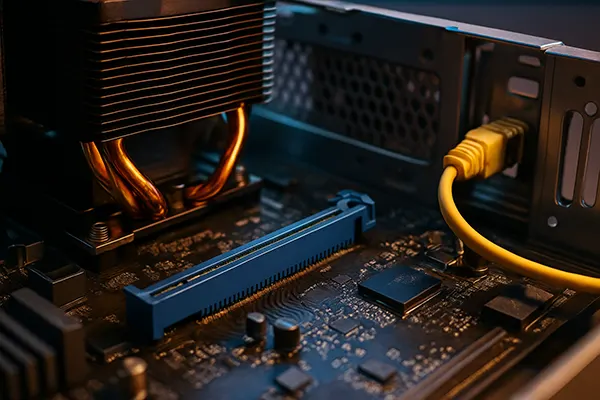

PCIe 6.0 und die Zukunft von Hochgeschwindigkeits-Computer-Schnittstellen

Die Entwicklung von PCI Express (PCIe) 6.0 stellt einen bedeutenden Meilenstein in der Evolution der Computerhardware-Konnektivität dar. Mit dem rasanten Wachstum datenintensiver Anwendungen wie Künstliche Intelligenz, High-Performance-Computing und Cloud-Infrastrukturen ist der Bedarf an höherer Bandbreite und geringerer Latenz entscheidend geworden. PCIe 6.0 verdoppelt die Übertragungsrate von PCIe 5.0 und bleibt gleichzeitig abwärtskompatibel, wodurch es sich als Schlüsseltechnologie für die nächste Generation des Computing positioniert.

Die technischen Fortschritte von PCIe 6.0

PCIe 6.0 bietet 64 GT/s Übertragungsgeschwindigkeit und verdoppelt damit den Durchsatz von PCIe 5.0. Dies wird durch den Einsatz von Pulse-Amplitude-Modulation mit vier Stufen (PAM4) erreicht – eine Technik, die auch in modernen Netzwerktechnologien verbreitet ist. Mit dieser Signalisierungsmethode kann PCIe 6.0 bis zu 256 GB/s bidirektionale Bandbreite auf einer 16-Lane-Konfiguration liefern.

Ein weiteres bemerkenswertes Merkmal ist die Implementierung von Forward Error Correction (FEC). Da PAM4 höhere Fehlerraten verursacht, sorgt FEC für Datenintegrität, ohne die Latenz wesentlich zu erhöhen. Dies ist besonders wichtig für Arbeitslasten, die auf Genauigkeit und Zuverlässigkeit angewiesen sind, wie etwa wissenschaftliches Rechnen oder das Training von Machine-Learning-Modellen.

Die Spezifikation unterstützt außerdem dynamische Link-Equalisierung und Latenzoptimierungen. Diese Verbesserungen ermöglichen es PCIe 6.0, höhere Leistung mit reduzierten Datenübertragungs-Engpässen zu verbinden und so einen reibungsloseren Ablauf bei massiv paralleler Datenverarbeitung sicherzustellen.

Kompatibilität und Integration

Eine der größten Stärken von PCIe war schon immer die Abwärtskompatibilität. Auch PCIe 6.0 setzt diesen Weg fort und erlaubt die Integration neuer Geräte, ohne dass ältere Hardware aufgegeben werden muss. Dadurch ist eine schrittweise Einführung in Branchen möglich, in denen die vollständige Erneuerung der Infrastruktur kostspielig wäre.

Hardwarehersteller wie Intel und AMD haben bereits Roadmaps veröffentlicht, die PCIe 6.0 in kommende Server- und Desktop-CPUs integrieren. Diese Unterstützung deutet auf eine beschleunigte Einführung in Rechenzentren, Gaming-Systemen und Unternehmensservern hin.

Auch Speicher- und Grafikkartenhersteller werden PCIe 6.0 voraussichtlich übernehmen, sobald die Nachfrage nach höherem Datendurchsatz steigt. Das Gleichgewicht zwischen Innovation und Kompatibilität bleibt für den Erfolg ausschlaggebend.

Anwendungen und Auswirkungen auf die Industrie

PCIe 6.0 wird zahlreiche Branchen verändern. In Rechenzentren ist die Fähigkeit, größere Datenmengen schneller zu verarbeiten, entscheidend für KI, Big-Data-Analysen und Hochfrequenzhandel. Diese Bereiche sind stark auf eine Reduzierung der Latenz angewiesen.

Für den Verbrauchermarkt wird PCIe 6.0 vor allem Grafikkarten, SSDs und Netzwerktechnik zugutekommen. Gamer, Content-Creator und Fachleute im Bereich 3D-Rendering oder Videobearbeitung werden deutliche Verbesserungen in der Systemreaktionszeit feststellen.

Auch in Telekommunikation und Edge-Computing ermöglicht PCIe 6.0 eine schnellere Datenverarbeitung in verteilten Netzwerken. Mit der Weiterentwicklung von 5G und künftigen Standards wird PCIe 6.0 eine Schlüsselrolle in digitalen Infrastrukturen einnehmen.

Herausforderungen bei der Einführung

Trotz des großen Potenzials gibt es Hürden. Die Komplexität der PAM4-Signalisierung erhöht die Entwicklungskosten und erfordert aufwändigere Tests. Dies führt zunächst zu höheren Hardwarepreisen.

Ein weiteres Problem ist die Balance zwischen Energieverbrauch und Leistung. Höhere Bandbreiten dürfen nicht zulasten der Energieeffizienz gehen. Hersteller müssen Innovationen entwickeln, um die Nachhaltigkeit zu gewährleisten.

Darüber hinaus hängt die breite Einführung davon ab, ob reale Anwendungen den Bedarf nach solch hohen Geschwindigkeiten erfordern. Solange Arbeitslasten nicht konsequent PCIe 6.0 ausschöpfen, bleibt der Nutzen zunächst auf Nischenmärkte wie Forschungseinrichtungen oder High-End-Server beschränkt.

Zukunftsperspektiven für Hochgeschwindigkeitsschnittstellen

Schon jetzt wird PCIe 7.0 diskutiert, das die Datenrate erneut verdoppeln soll. Doch jeder neue Standard bringt wachsende technische Herausforderungen und Kosten mit sich, was Unternehmen zu hybriden Ansätzen zwingt, die Leistung, Energieeffizienz und Kosten ausbalancieren.

Gleichzeitig entstehen ergänzende Standards wie CXL (Compute Express Link), das auf PCIe aufbaut und eine effizientere Ressourcennutzung zwischen CPUs, GPUs und Beschleunigern ermöglicht. Die Zukunft wird daher nicht von einer einzigen Schnittstelle bestimmt, sondern von einem Zusammenspiel mehrerer Technologien.

Bis 2030 werden Hochgeschwindigkeitsverbindungen wie PCIe 6.0 zentrale Bestandteile von KI, Cloud-Anwendungen und Simulationen sein. Auch in autonomen Fahrzeugen oder der intelligenten Fertigung wird Echtzeit-Datenaustausch unverzichtbar.

Die Rolle von Standardisierungsorganisationen

Die PCI-SIG (PCI Special Interest Group) ist die maßgebliche Organisation hinter der Entwicklung von PCIe. Ihr kollaboratives Modell mit Branchenführern, Halbleiterfirmen und Hardwareherstellern ermöglicht eine weltweite Umsetzung.

Standardisierung garantiert nicht nur Kompatibilität, sondern beschleunigt auch Innovationen, da ein klarer Fahrplan für Forschung und Entwicklung existiert. So können Fortschritte in PCIe-Technologie zuverlässig und praxisnah umgesetzt werden.

Mit der Ratifizierung von PCIe 6.0 und den ersten Hardwarelösungen ist der Standard bereit, eine entscheidende Rolle bei der Weiterentwicklung von Computing-Infrastrukturen in diesem Jahrzehnt zu spielen.